ウルトラ高性能な「Apple M1 Ultra」の謎:大原雄介のエレ・組み込みプレイバック(4/4 ページ)

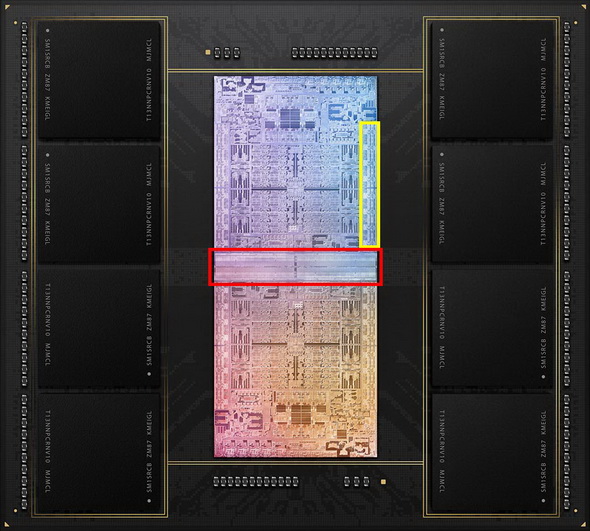

なんでこの方式を使ったと筆者が考えているか? というと、Photo02の赤枠部は多分これインターポーザ用ではない、と考えられるからだ。要するに大きすぎるのである。そもそもインターポーザを使う場合、信号の電圧はかなり低く抑えられるのがメリットである。とはいっても例えばTSVほどには下げられないのだが、送受信を行うPHY(物理層)はかなり小さい。TSMCのCoWoSを使う製品は現在非常に多いが、そのCoWoS用のPHYにこんなに面積を割いている製品は他に見たことがない。単に幅広いだけではなく、縦方向にも長いのが特徴的である。なにせ面積で言えば、黄色い枠で囲ったLPDDR5 256bit(32×8)用のPHYよりもデカいのだから、これは相当なものである。インターポーザ方式のメリットの一つは巨大なPHYが必要ない事なので、どう考えてもこれはインターポーザではない。

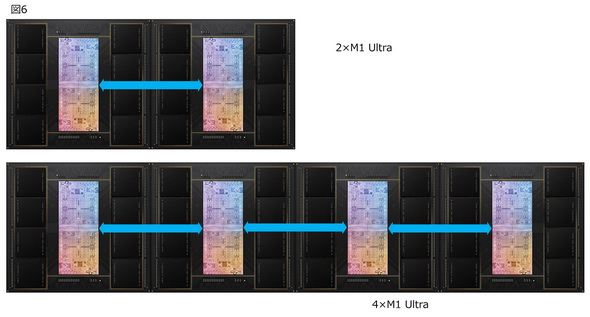

ではこれは何か? 筆者は、これはCPU接続用の高速Interconnect用のPHYだと考えている。そしてM1 MAXでは恐らくこのInterconnectは使わず、前ページで示した特許の仕組みを使って2つのチップを接続していると考えている。ではこのInterconnectは? というと4チップ以上の接続用であろう。Intelで言えばUPIとかMDI(Multi-Die Fabric IO)、AMDのInfinity Fabric、NVIDIAのNVLinkなどにあたるものだ。これが図6の様に接続される形になる。LPDDR5の配されているパッケージの下を、相互接続用Interconnectが走る格好だろう。こうしたInterconnect用、と考えればこの謎のエリアの大きさも納得がいく。

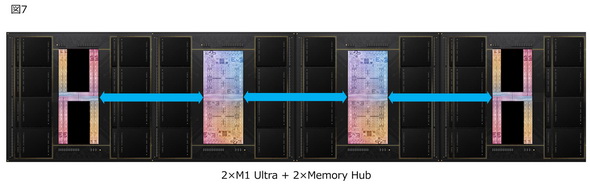

この方式の問題は、メモリ容量である。M1 Ultra1個当たり128GBだから、4つ並べても512GBでしかない。一つの解は、こうした大容量向けにメモリベンダーが頑張って、32GB LPDDR5を投入する(これによりメモリ容量が倍になる)というもの。もう一つは、このInterconnectの先に、メモリコントローラのみ載せた、いわゆるMemory Hub的なものがぶら下がる可能性だ。LPDDR5チップの場合発熱が非常に小さいからスタッキング、つまり複数のメモリチップを積み重ねる事も現実的である。図7は2段スタッキングしたMemory Hubを両側にぶら下げた例だが、この構成ならMemory Hub当たり256GB、システム全体で768GBになる。4段スタッキングならMemory Hub当たり512GB、システム全体で1.25TBほどになる。つまり、方法としてはいろいろやりようがある訳だ。

実際のところどうなのか? というのは神のみぞ知るという話だが、一応こうした構造が考えられるという一つの仮説を今回はご紹介した。

関連記事

Intelの工場新設やTSMC/UMC/Samsungの巨額投資、半導体各社が生産能力拡充

Intelの工場新設やTSMC/UMC/Samsungの巨額投資、半導体各社が生産能力拡充

エレクトロニクス/組み込み業界の動向をウオッチする連載。今回は、この1〜2カ月で目立った話題として、Fabやメモリベンダーの相次ぐ生産能力拡充の話についてお届けする。 TSMCは日本で何をしようとしているのか

TSMCは日本で何をしようとしているのか

エレクトロニクス/組み込み業界の動向をウオッチする連載。今回は、2021年2月にテレビ報道でも話題(?)となった「TSMCの日本進出の意図」についてお届けする。 AMDによるXilinx買収、両社のメリットと思惑

AMDによるXilinx買収、両社のメリットと思惑

エレクトロニクス/組み込み業界の動向をウオッチする連載。今回は、2020年10月の業界動向の振り返りとして、AMDによるXilinx買収の話題をお届けする。 黄昏の時期に入ったx86

黄昏の時期に入ったx86

エレクトロニクス/組み込み業界の動向をウオッチする連載。今回は、2020年を通して振り返ってみて感じた「x86」への筆者の見解をお届けする。 Arm再売却の予想と、Intel TMGの行方

Arm再売却の予想と、Intel TMGの行方

エレクトロニクス/組み込み業界の動向をウオッチする連載。今回は、2020年7月の業界動向の振り返りとして、SoftBankがArmの売却に動いている件についての見解と、Intelの半導体製造を担うTMG(Technology and Manufacturing Group)についてお届けする。 Appleは訴えたのにAMDは見逃し、GLOBALFOUNDRIESによるTSMC提訴の背景

Appleは訴えたのにAMDは見逃し、GLOBALFOUNDRIESによるTSMC提訴の背景

エレクトロニクス/組み込み業界の動向をウオッチする連載。今回は、2019年8月の業界動向の振り返りとして、GLOBALFOUNDRIESによるTSMCおよび顧客企業への訴訟とその背景を考察する。

Copyright © ITmedia, Inc. All Rights Reserved.

会員登録がまだの方はこちら

豊富なホワイトペーパーの中から、製品・サービス導入の検討に役立つ技術情報や導入事例などを簡単に入手できます。

特集

- 設計者CAEの取り組みに関する実態

- マテリアルズ・インフォマティクスの動向調査

- 製造業のアナログ業務の実態調査

- 設計・解析業務におけるAI活用

- 製造現場におけるデータ活用の実態調査

- 3Dプリンタ利用動向調査

- CAD利用動向調査

- 研究・開発職のデジタル活用調査

- 安全安心なIoT機器実現の課題

- 電気設計者の課題と解決

- “つながる工場”の現状と課題

- 製造業におけるAI開発および活用の実態

- 設計・製造現場における品質管理

- 製造業IoTセキュリティ

- IoT時代の組み込みソフトウェア品質

- IoT時代のセキュリティリスクに備える

- 加速する工場と生産設備のデジタル化

- 製造業の省エネ対策と課題

- モノづくり設計者のワークスタイル調査

- タイアップ&セミナーコンテンツ一覧