ミリ波回路を高精度に設計、55nm CMOSデザインキット:三重富士通 ミリ波向け 55nm CMOS PDK

三重富士通セミコンダクターは、増幅器や周波数変換回路などのミリ波回路を含む大規模回路を、短期間かつ高精度に設計できる55nm CMOS プロセスデザインキット(PDK)を開発。提供を開始した。

三重富士通セミコンダクターは2018年1月11日、富士通研究所と共同で、車載レーダーや5G(第5世代移動通信)などのミリ波市場向けに、高精度の回路設計ができる55nm CMOSプロセスデザインキット(PDK)を開発し、提供を開始したと発表した。同PDKを用いることで、増幅器や周波数変換回路など複数のミリ波回路を含む大規模回路を、効率的かつ高精度に設計できるようになるとする。

車載レーダーや5Gへの注目の高まりとともに、ミリ波帯において低消費電力で動作するCMOS回路への関心も高まっている。ただし、波長が短いミリ波帯では精度のよい素子モデルの実現が難しく、回路試作を何度も繰り返しがら要求性能を引き出していく必要があった。そのため、開発期間も試作コストも増大してしまうという課題があったという。

今回提供を開始したPDKは、55nmベースの技術「C55LP(Low Power)および、三重富士通セミコンダクター独自の超低消費電力テクノロジー「C55DDC(Deeply Depleted Channel)」で、ミリ波帯設計に最適化したもの。素子パラメーターやレイアウト構造をミリ波帯に最適化したトランジスタや伝送線路などを含み、100GHz以下の周波数帯で大規模なトランシーバー回路を精度よく設計できるとする。

同PDKでは、最大110GHzまでシリコン検証されたミリ波用SPICEモデルを使用している。ミリ波用トランジスタの他、伝送線路、インダクター、抵抗、ダイオードなどの素子の特性も最適化した。主要なEDAベンダーのツールをサポートしていて、対応する周波数帯は28GHz、80GHzである。

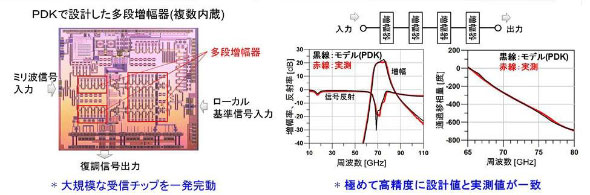

上の図版左は、受信回路である。ミリ波帯信号を高利得に増幅する「多段増幅器」、多重化された2本の信号を高精度に分離、復調する「直交復調器」で構成される。多段増幅器は段数を連ねるごとに設計値と実測値の乖離(かいり)が大きくなり、ミリ波帯で精度よく設計することが困難だった。今回開発したPDKを利用することで、極めて精度よく多段増幅器を設計できるようになるという。

さらに、増幅器だけでなく、広帯域な直交復調器や周波数変換器、電圧制御発振器など、ミリ波回路全般の設計精度を高めることも可能だとする。このため、大規模なミリ波帯送受信回路を短期間で開発できるようになる。

三重富士通セミコンダクターは、パッケージングまでを考慮したミリ波PDKの準備も進めている。アナログ回路マクロやミリ波帯素子評価などの周辺サービスを含め、2018年度から順次提供を開始する予定だ。

関連記事

「AIチップの単純な機能競争に意味は薄い」、クアルコム幹部が語る

「AIチップの単純な機能競争に意味は薄い」、クアルコム幹部が語る

NXPの買収を進めるクアルコムの幹部が来日、同社の事業戦略を語った。半導体企業の新要素として期待されるAIについては「電力もしくは価格当たりの効率性能が大きな意味を持つ」と、モバイルで鍛えられた企業ならではの見解を示した。 48Gbpsの広帯域に対応するHDMI最新規格、CTSは2018年第一四半期から順次配布

48Gbpsの広帯域に対応するHDMI最新規格、CTSは2018年第一四半期から順次配布

HDMIフォーラムはHDMI(High-Definition Multimedia Interface)の最新規格である「2.1」を発表した。最高で48Gbpsの帯域幅に対応しており、コンプライアンステスト仕様書(CTS)は2018年第1四半期〜第3四半期にかけて段階的に提供される。 産業用IoT向けのダイナミックNFCタグIC

産業用IoT向けのダイナミックNFCタグIC

amsが産業用IoT向けのダイナミックNFCタグIC「AS3956」を発表した。NFCフォーラム仕様に準拠したNDEFメッセージングプロトコルをサポートし、NFC対応携帯電話との相互運用性を備えている。 グローバルシャッター搭載の1.0MピクセルCMOSセンサー

グローバルシャッター搭載の1.0MピクセルCMOSセンサー

オン・セミコンダクターは、グローバルシャッターを備えた、1/4型、1.0MピクセルのCMOSデジタルイメージセンサー「AR0144」を発表した。低照度から高照度条件まで、ノイズのない鮮明かつ正確な画像を高速で撮像できる。 6自由度で検出する産業用慣性計測ユニット

6自由度で検出する産業用慣性計測ユニット

アナログ・デバイセズ(ADI)は、産業用慣性計測ユニット5製品を発表した。3軸MEMS加速度センサーおよび、ジャイロスコープにより、6DoF(6自由度)で検出する。

Copyright © ITmedia, Inc. All Rights Reserved.

会員登録がまだの方はこちら

豊富なホワイトペーパーの中から、製品・サービス導入の検討に役立つ技術情報や導入事例などを簡単に入手できます。

特集

- 設計者CAEの取り組みに関する実態

- マテリアルズ・インフォマティクスの動向調査

- 製造業のアナログ業務の実態調査

- 設計・解析業務におけるAI活用

- 製造現場におけるデータ活用の実態調査

- 3Dプリンタ利用動向調査

- CAD利用動向調査

- 研究・開発職のデジタル活用調査

- 安全安心なIoT機器実現の課題

- 電気設計者の課題と解決

- “つながる工場”の現状と課題

- 製造業におけるAI開発および活用の実態

- 設計・製造現場における品質管理

- 製造業IoTセキュリティ

- IoT時代の組み込みソフトウェア品質

- IoT時代のセキュリティリスクに備える

- 加速する工場と生産設備のデジタル化

- 製造業の省エネ対策と課題

- モノづくり設計者のワークスタイル調査

- タイアップ&セミナーコンテンツ一覧