ニュース

テスト時間を3分の1に短縮できるSoC設計テストツール:Cadense Design Modus Test Solution

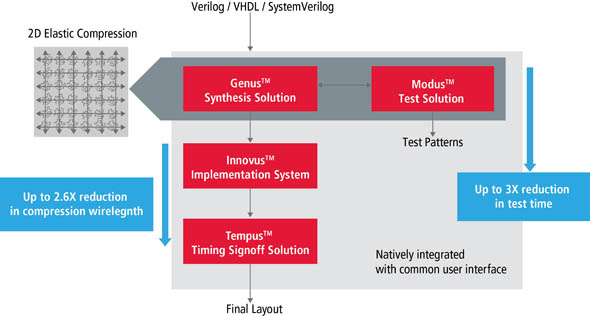

ケイデンスはSoC設計テストツール「Modus Test Solution」を発表。SoC設計のテスト時間を大幅に短縮できるという。

Cadense Design Systemsは2016年2月2日(米国時間)、SoC(System on Chip)設計のテスト時間を「最短で3分の1に短縮可能」(同社)なテストツール「Modus Test Solution」を発表した。

◎「組み込みソフトウェア品質」関連記事 〜事例、ツール、ソリューション、課題〜 など

新ツールは「2D Elastic Compression」と呼ぶアーキテクチャの導入により、デザインサイズや配線に影響を与えずに400倍を超える圧縮率を実現しており、加えて、ATPG(automatic test pattern generation)の実行中に複数スキャンサイクルをまたいだケアビット制御が可能であることから、高圧縮であっても高い故障検出率を維持している。

またIPコア内蔵メモリのセルフテスト(PMBIST)実行時にシェアードテストアクセスバスを挿入可能であり、FinFET SRAMや自動車の安全性アプリケーションなどのテストアルゴリズムも挿入できる。DFTロジックやGenusなどで共有される新しく統合されたTCLスクリプト記述およびデバッグ環境を用いるATPG機能も用意されている。

Copyright © ITmedia, Inc. All Rights Reserved.