ƒ~ƒٹ”g‰ٌکH‚ًچ‚گ¸“x‚ةگفŒvپA55nm CMOSƒfƒUƒCƒ“ƒLƒbƒgپFژOڈd•xژm’ت ƒ~ƒٹ”gŒü‚¯ 55nm CMOS PDK

ژOڈd•xژm’تƒZƒ~ƒRƒ“ƒ_ƒNƒ^پ[‚حپA‘•ٹي‚âژü”gگ”•دٹ·‰ٌکH‚ب‚ا‚جƒ~ƒٹ”g‰ٌکH‚ًٹـ‚ق‘ه‹K–ح‰ٌکH‚ًپA’Zٹْٹش‚©‚آچ‚گ¸“x‚ةگفŒv‚إ‚«‚é55nm CMOS ƒvƒچƒZƒXƒfƒUƒCƒ“ƒLƒbƒgپiPDKپj‚ًٹJ”پB’ٌ‹ں‚ًٹJژn‚µ‚½پB

پ@ژOڈd•xژm’تƒZƒ~ƒRƒ“ƒ_ƒNƒ^پ[‚ح2018”N1Œژ11“ْپA•xژm’تŒ¤‹†ڈٹ‚ئ‹¤“¯‚إپAژشچعƒŒپ[ƒ_پ[‚â5Gپi‘و5گ¢‘مˆع“®’تگMپj‚ب‚ا‚جƒ~ƒٹ”gژsڈêŒü‚¯‚ةپAچ‚گ¸“x‚ج‰ٌکHگفŒv‚ھ‚إ‚«‚é55nm CMOSƒvƒچƒZƒXƒfƒUƒCƒ“ƒLƒbƒgپiPDKپj‚ًٹJ”‚µپA’ٌ‹ں‚ًٹJژn‚µ‚½‚ئ”•\‚µ‚½پB“¯PDK‚ً—p‚¢‚邱‚ئ‚إپA‘•ٹي‚âژü”gگ”•دٹ·‰ٌکH‚ب‚ا•،گ”‚جƒ~ƒٹ”g‰ٌکH‚ًٹـ‚ق‘ه‹K–ح‰ٌکH‚ًپAŒّ—¦“I‚©‚آچ‚گ¸“x‚ةگفŒv‚إ‚«‚é‚و‚¤‚ة‚ب‚é‚ئ‚·‚éپB

پ@ژشچعƒŒپ[ƒ_پ[‚â5G‚ض‚ج’چ–ع‚جچ‚‚ـ‚è‚ئ‚ئ‚à‚ةپAƒ~ƒٹ”g‘ر‚ة‚¨‚¢‚ؤ’لڈء”ï“d—ح‚إ“®چى‚·‚éCMOS‰ٌکH‚ض‚جٹضگS‚àچ‚‚ـ‚ء‚ؤ‚¢‚éپB‚½‚¾‚µپA”g’·‚ھ’Z‚¢ƒ~ƒٹ”g‘ر‚إ‚حگ¸“x‚ج‚و‚¢‘fژqƒ‚ƒfƒ‹‚جژہŒ»‚ھ“‚پA‰ٌکHژژچى‚ً‰½“x‚àŒJ‚è•ش‚µ‚ھ‚ç—v‹پگ«”\‚ًˆّ‚«ڈo‚µ‚ؤ‚¢‚•K—v‚ھ‚ ‚ء‚½پB‚»‚ج‚½‚كپAٹJ”ٹْٹش‚àژژچىƒRƒXƒg‚à‘‘ه‚µ‚ؤ‚µ‚ـ‚¤‚ئ‚¢‚¤‰غ‘è‚ھ‚ ‚ء‚½‚ئ‚¢‚¤پB

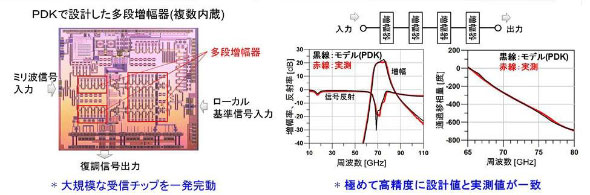

چ،‰ٌٹJ”‚µ‚½PDK‚إگفŒv‚µ‚½ژَگM‰ٌکHپiچ¶پj‚ئŒv‘ھŒ‹‰ت ڈo“TپFژOڈd•xژm’تƒZƒ~ƒRƒ“ƒ_ƒNƒ^پ[پiƒNƒٹƒbƒN‚إٹg‘هپj

پƒvƒŒƒ~ƒAƒ€ƒRƒ“ƒeƒ“ƒc

گV’…

» ‘g‚فچ‚فƒGƒ“ƒWƒjƒA‚ج7ٹ„‚ھپu“]گE‚µ‚ؤ‚à‚¢‚¢پvپAƒ_ƒ“ƒgƒc——R‚ج‘و1ˆت‚حپ@

» ژںگ¢‘مگ»‘¢‹ئ‚جژہŒ»‚ةŒü‚¯پAGE‚ھ’§گي‚·‚é3‚آ‚جƒfƒWƒ^ƒ‹•دٹvپ@

» HPE‚ھƒXƒ}پ[ƒgچHڈê‚جژہŒ»‚ةŒü‚¯‚ؤ’ٌڈ¥‚·‚éپuƒVƒtƒgƒŒƒtƒgپv‚ئ‚¢‚¤چl‚¦•ûپ@

» گ»‘¢‹ئ‚جگ§Œنڈî•ٌŒnƒVƒXƒeƒ€‚ًƒTƒCƒoپ[چUŒ‚‚©‚çژç‚éپuITƒZƒLƒ…ƒٹƒeƒB‚ج—حپvپ@

پ@چ،‰ٌ’ٌ‹ں‚ًٹJژn‚µ‚½PDK‚حپA55nmƒxپ[ƒX‚ج‹ZڈpپuC55LPپiLow Powerپj‚¨‚و‚رپAژOڈd•xژm’تƒZƒ~ƒRƒ“ƒ_ƒNƒ^پ[“ئژ©‚ج’´’لڈء”ï“d—حƒeƒNƒmƒچƒWپ[پuC55DDCپiDeeply Depleted Channelپjپv‚إپAƒ~ƒٹ”g‘رگفŒv‚ةچإ“K‰»‚µ‚½‚à‚جپB‘fژqƒpƒ‰ƒپپ[ƒ^پ[‚⃌ƒCƒAƒEƒgچ\‘¢‚ًƒ~ƒٹ”g‘ر‚ةچإ“K‰»‚µ‚½ƒgƒ‰ƒ“ƒWƒXƒ^‚â“`‘—گüکH‚ب‚ا‚ًٹـ‚فپA100GHzˆب‰؛‚جژü”gگ”‘ر‚إ‘ه‹K–ح‚بƒgƒ‰ƒ“ƒVپ[ƒoپ[‰ٌکH‚ًگ¸“x‚و‚گفŒv‚إ‚«‚é‚ئ‚·‚éپB

پ@“¯PDK‚إ‚حپAچإ‘ه110GHz‚ـ‚إƒVƒٹƒRƒ“Œںڈط‚³‚ꂽƒ~ƒٹ”g—pSPICEƒ‚ƒfƒ‹‚ًژg—p‚µ‚ؤ‚¢‚éپBƒ~ƒٹ”g—pƒgƒ‰ƒ“ƒWƒXƒ^‚ج‘¼پA“`‘—گüکHپAƒCƒ“ƒ_ƒNƒ^پ[پA’ïچRپAƒ_ƒCƒIپ[ƒh‚ب‚ا‚ج‘fژq‚ج“ءگ«‚àچإ“K‰»‚µ‚½پBژه—v‚بEDAƒxƒ“ƒ_پ[‚جƒcپ[ƒ‹‚ًƒTƒ|پ[ƒg‚µ‚ؤ‚¢‚ؤپA‘خ‰‚·‚éژü”gگ”‘ر‚ح28GHzپA80GHz‚إ‚ ‚éپB

پ@ڈم‚جگ}”إچ¶‚حپAژَگM‰ٌکH‚إ‚ ‚éپBƒ~ƒٹ”g‘رگMچ†‚ًچ‚—ک“¾‚ة‘•‚·‚éپu‘½’i‘•ٹيپvپA‘½ڈd‰»‚³‚ꂽ2–{‚جگMچ†‚ًچ‚گ¸“x‚ة•ھ—£پA•œ’²‚·‚éپu’¼Œً•œ’²ٹيپv‚إچ\گ¬‚³‚ê‚éپB‘½’i‘•ٹي‚ح’iگ”‚ًکA‚ث‚邲‚ئ‚ةگفŒv’l‚ئژہ‘ھ’l‚جک¨—£پi‚©‚¢‚èپj‚ھ‘ه‚«‚‚ب‚èپAƒ~ƒٹ”g‘ر‚إگ¸“x‚و‚گفŒv‚·‚邱‚ئ‚ھچ¢“‚ء‚½پBچ،‰ٌٹJ”‚µ‚½PDK‚ً—ک—p‚·‚邱‚ئ‚إپA‹ة‚ك‚ؤگ¸“x‚و‚‘½’i‘•ٹي‚ًگفŒv‚إ‚«‚é‚و‚¤‚ة‚ب‚é‚ئ‚¢‚¤پB

پ@‚³‚ç‚ةپA‘•ٹي‚¾‚¯‚إ‚ب‚پAچL‘رˆو‚ب’¼Œً•œ’²ٹي‚âژü”gگ”•دٹ·ٹيپA“dˆ³گ§Œن”گUٹي‚ب‚اپAƒ~ƒٹ”g‰ٌکH‘S”ت‚جگفŒvگ¸“x‚ًچ‚‚ك‚邱‚ئ‚à‰آ”\‚¾‚ئ‚·‚éپB‚±‚ج‚½‚كپA‘ه‹K–ح‚بƒ~ƒٹ”g‘ر‘—ژَگM‰ٌکH‚ً’Zٹْٹش‚إٹJ”‚إ‚«‚é‚و‚¤‚ة‚ب‚éپB

پ@ژOڈd•xژm’تƒZƒ~ƒRƒ“ƒ_ƒNƒ^پ[‚حپAƒpƒbƒPپ[ƒWƒ“ƒO‚ـ‚إ‚ًچl—¶‚µ‚½ƒ~ƒٹ”gPDK‚جڈ€”ُ‚àگi‚ك‚ؤ‚¢‚éپBƒAƒiƒچƒO‰ٌکHƒ}ƒNƒچ‚âƒ~ƒٹ”g‘ر‘fژq•]‰؟‚ب‚ا‚جژü•سƒTپ[ƒrƒX‚ًٹـ‚كپA2018”N“x‚©‚çڈ‡ژں’ٌ‹ں‚ًٹJژn‚·‚é—\’肾پB

Copyright © ITmedia, Inc. All Rights Reserved.

ٹضکA‹Lژ–

پuAIƒ`ƒbƒv‚ج’Pڈƒ‚ب‹@”\‹£‘ˆ‚ةˆس–،‚ح”–‚¢پvپAƒNƒAƒ‹ƒRƒ€ٹ²•”‚ھŒê‚é

پuAIƒ`ƒbƒv‚ج’Pڈƒ‚ب‹@”\‹£‘ˆ‚ةˆس–،‚ح”–‚¢پvپAƒNƒAƒ‹ƒRƒ€ٹ²•”‚ھŒê‚é

NXP‚ج”ƒژû‚ًگi‚ك‚éƒNƒAƒ‹ƒRƒ€‚جٹ²•”‚ھ—ˆ“ْپA“¯ژذ‚جژ–‹ئگي—ھ‚ًŒê‚ء‚½پB”¼“±‘جٹé‹ئ‚جگV—v‘f‚ئ‚µ‚ؤٹْ‘ز‚³‚ê‚éAI‚ة‚آ‚¢‚ؤ‚حپu“d—ح‚à‚µ‚‚ح‰؟ٹi“–‚½‚è‚جŒّ—¦گ«”\‚ھ‘ه‚«‚بˆس–،‚ًژ‚آپv‚ئپAƒ‚ƒoƒCƒ‹‚إ’b‚¦‚ç‚ꂽٹé‹ئ‚ب‚ç‚إ‚ح‚جŒ©‰ً‚ًژ¦‚µ‚½پB 48Gbps‚جچL‘رˆو‚ة‘خ‰‚·‚éHDMIچإگV‹KٹiپACTS‚ح2018”N‘وˆêژl”¼ٹْ‚©‚çڈ‡ژں”z•z

48Gbps‚جچL‘رˆو‚ة‘خ‰‚·‚éHDMIچإگV‹KٹiپACTS‚ح2018”N‘وˆêژl”¼ٹْ‚©‚çڈ‡ژں”z•z

HDMIƒtƒHپ[ƒ‰ƒ€‚حHDMIپiHigh-Definition Multimedia Interfaceپj‚جچإگV‹Kٹi‚إ‚ ‚éپu2.1پv‚ً”•\‚µ‚½پBچإچ‚‚إ48Gbps‚ج‘رˆو•‚ة‘خ‰‚µ‚ؤ‚¨‚èپAƒRƒ“ƒvƒ‰ƒCƒAƒ“ƒXƒeƒXƒgژd—lڈ‘پiCTSپj‚ح2018”N‘و1ژl”¼ٹْپ`‘و3ژl”¼ٹْ‚ة‚©‚¯‚ؤ’iٹK“I‚ة’ٌ‹ں‚³‚ê‚éپB ژY‹ئ—pIoTŒü‚¯‚جƒ_ƒCƒiƒ~ƒbƒNNFCƒ^ƒOIC

ژY‹ئ—pIoTŒü‚¯‚جƒ_ƒCƒiƒ~ƒbƒNNFCƒ^ƒOIC

ams‚ھژY‹ئ—pIoTŒü‚¯‚جƒ_ƒCƒiƒ~ƒbƒNNFCƒ^ƒOICپuAS3956پv‚ً”•\‚µ‚½پBNFCƒtƒHپ[ƒ‰ƒ€ژd—l‚ةڈ€‹’‚µ‚½NDEFƒپƒbƒZپ[ƒWƒ“ƒOƒvƒچƒgƒRƒ‹‚ًƒTƒ|پ[ƒg‚µپANFC‘خ‰Œg‘ر“dکb‚ئ‚ج‘ٹŒف‰^—pگ«‚ً”ُ‚¦‚ؤ‚¢‚éپB ƒOƒچپ[ƒoƒ‹ƒVƒƒƒbƒ^پ[“‹چع‚ج1.0MƒsƒNƒZƒ‹CMOSƒZƒ“ƒTپ[

ƒOƒچپ[ƒoƒ‹ƒVƒƒƒbƒ^پ[“‹چع‚ج1.0MƒsƒNƒZƒ‹CMOSƒZƒ“ƒTپ[

ƒIƒ“پEƒZƒ~ƒRƒ“ƒ_ƒNƒ^پ[‚حپAƒOƒچپ[ƒoƒ‹ƒVƒƒƒbƒ^پ[‚ً”ُ‚¦‚½پA1/4Œ^پA1.0MƒsƒNƒZƒ‹‚جCMOSƒfƒWƒ^ƒ‹ƒCƒپپ[ƒWƒZƒ“ƒTپ[پuAR0144پv‚ً”•\‚µ‚½پB’لڈئ“x‚©‚çچ‚ڈئ“xڈًŒڈ‚ـ‚إپAƒmƒCƒY‚ج‚ب‚¢‘N–¾‚©‚آگ³ٹm‚ب‰و‘œ‚ًچ‚‘¬‚إژB‘œ‚إ‚«‚éپB 6ژ©—R“x‚إŒںڈo‚·‚éژY‹ئ—pٹµگ«Œv‘ھƒ†ƒjƒbƒg

6ژ©—R“x‚إŒںڈo‚·‚éژY‹ئ—pٹµگ«Œv‘ھƒ†ƒjƒbƒg

ƒAƒiƒچƒOپEƒfƒoƒCƒZƒYپiADIپj‚حپAژY‹ئ—pٹµگ«Œv‘ھƒ†ƒjƒbƒg5گ»•i‚ً”•\‚µ‚½پB3ژ²MEMS‰ء‘¬“xƒZƒ“ƒTپ[‚¨‚و‚رپAƒWƒƒƒCƒچƒXƒRپ[ƒv‚ة‚و‚èپA6DoFپi6ژ©—R“xپj‚إŒںڈo‚·‚éپB