基材や形状を選ばない非真空ドライめっき技術:FLOSFIA ミストドライ めっき法

ベンチャー企業のFLOSFIAは、京都大学が開発した薄膜形成技術「ミストCVD法」を発展させ、基材の種類や形状に関係なく金属薄膜を成膜できる非真空ドライめっき技術「ミストドライ めっき法」を開発した。10μm以下の表面形状にも成膜可能で、半導体素子などの電極への応用が見込まれる。

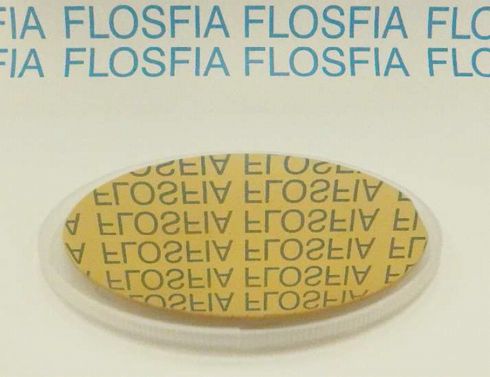

京都大学発のベンチャー企業であるFLOSFIAが2017年4月24日、基材の種類や形状に関係なくさまざまな金属薄膜を成膜できる非真空ドライめっき技術「ミストドライ めっき法」を開発したと発表した。10μm以下の表面形状への成膜が可能なことから、半導体素子や電子部品、MEMSなどの電極への応用が期待できる。

ミストドライ めっき法は、京都大学が開発した薄膜形成技術「ミストCVD法」を発展させたものだ。真空装置が不要のため、低コスト低エネルギーでの活用が可能。また、シアン化合物などの環境汚染物質を使用せず、廃液処理も必要ないので、従来の湿式メッキ技術と違って環境に優しい。

この手法で作成できる薄膜は、金、銅、ニッケル、ロジウムなどの金属単体にとどまらない。金-ニッケルなどの合金の他、多元合金にも及ぶ。また、サファイア基板などの結晶性基板、ステンレス板やアルミ板などの金属板、電気の流れない基材など、成膜できる基材の種類も幅広い。ポリイミドフィルム上へのロジウム成膜も実現できる。

基材の種類を問わないだけでなく、複雑な形状の基材への成膜も可能。例えば、幅2μm深さ1μmの微小な溝がある凹凸表面に、被覆性よく金の薄膜を成膜することに成功している。また、直径200nm程度のSiO2粉末上に均一な金の薄膜を成膜した実績がある。

このように、従来の湿式メッキでは不可能な10μm以下の表面形状へも金属成膜できるため、半導体素子や電子部品、MEMSなどの電極への応用が見込まれる。例えば、MEMS基板の微細ビアの導通や、溝を埋める電極形成の他、IoT向け極小センサーの電極への追従性に優れた薄膜の形成などに活用できる。

FLOSFIAは今後、ミストドライ めっき法のテスト成膜と共同開発を開始する。また、同手法で作成した各種材料の製造販売を2019年に開始する予定としている。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

OLED向けのムラ補正IC、半導体メーカーと共同開発

OLED向けのムラ補正IC、半導体メーカーと共同開発

サイバネットシステムが半導体メーカーと共同で、有機ELディスプレイ(OLED)向けのムラ補正IPを含むディスプレイドライバICを開発した。2017年6月ごろから販売の予定。 大容量eMMC向け高速自動プログラミングシステム、最高1300個/時を生産

大容量eMMC向け高速自動プログラミングシステム、最高1300個/時を生産

東陽テクニカが大容量eMMCに適した高速書き込みシステム「PSV5000/LX」(米Date I/O製)を販売開始した。最高80MB/秒の書き込みで、最高1300個/時の生産が可能だ。 FPGAの性能を強化する「Lattice Diamond」

FPGAの性能を強化する「Lattice Diamond」

ラティスセミコンダクターは、FPGA用設計ツール「Lattice Diamond」のバージョン3.7を公開したと発表した。ECP5/MachXO2/MachXO3 FPGAファミリーの性能を強化している。 回路設計ソフトウェア「Multisim」のWeb対応版を発表

回路設計ソフトウェア「Multisim」のWeb対応版を発表

日本ナショナルインスツルメンツ(NI)は、Webベースで回路図の入力とシミュレーションが行えるSPICEシミュレーション環境「Multisim Live」のβ版を発表した。 Faraday Technology、パッケージ設計期間を最大60%短縮

Faraday Technology、パッケージ設計期間を最大60%短縮

Faraday Technologyは、ケイデンス・デザイン・システムズの「OrbitIO Interconnect Designer」と「SiP Layout」を採用し、パッケージ設計時間を従来手法と比較して、最大60%短縮した。