CMOSイメージセンサーにDRAMを積層、3層構造をソニーが世界初:ソニー DRMA積層型イメージセンサー

ソニーは、DRAMを積層した3層構造の積層型CMOSイメージセンサーを開発した。高速読み出しを実現したことで、スマートフォンでもスーパースローモーション動画の撮影などが可能となる。

1930万画素の静止画を120分の1秒で読み出し

ソニーは2017年2月、DRAMを積層した3層構造の積層型CMOSイメージセンサーを開発したと発表した。高速読み出しを実現し、フルHDサイズで毎秒最大1000フレームというスーパースローモーション動画の撮影を可能とした。

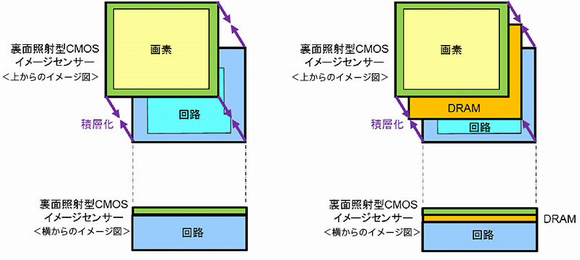

ソニーはこれまで、裏面照射型画素部分と信号処理回路部分を積層し、2層構造としたCMOSイメージセンサーを供給してきた。今回は画素部と回路部の間に、容量が1GビットのDRAMを追加し3層構造とした。「DRAMを積層した3層構造のCMOSイメージセンサーは業界で初めて」と主張する。

開発品は、撮影した画像の読み出しを高速に行うため、画素部分から読み出したアナログ映像信号をデジタル信号へ変換する回路を、従来の2段から4段構造に増やした。また、読み出した信号をいったんDRAMに保存することで、業界標準のインタフェース規格に対応した速度で信号を出力することができるようにした。3層にそれぞれ搭載された回路間のノイズを低減する工夫も行うなど、高機能化とともに高い品質と信頼性も確保している。

開発したイメージセンサーの主な仕様は、有効画素数が2120万画素(5520×3840画素)、イメージサイズは対角7.73mm(1/2.3型)、ユニットセルサイズは1.22×1.22μmである。

こうした工夫により、1930万画素の静止画であれば、1枚当たり120分の1秒のスピードで読み出すことができる。従来に比べ約4倍の高速読み出しを実現した。これにより、メカニカルシャッターを備えていないスマートフォンのカメラモジュールなどで、動きの速い被写体を撮影した場合でも、フォーカルプレーンひずみを抑えた静止画の撮影が可能となる。

高速読み出し技術は動画撮影時も有用だ。フルHD(1920×1080画素)サイズで毎秒最大1000フレーム(従来比で約8倍)のスーパースローモーション動画を撮影することが可能となる。DRAMに蓄積した高速撮影データと、通常速度で撮影した動画データを出力し、外付けの画像処理回路(ISP)で信号処理すれば、通常の動画とスーパースローモーション動画をシームレスにつないだユニークな動画作品を、スマートフォンで撮影することもできる。被写体の急激な変化を検知して、高速撮影を自動で開始する設定も可能だという。

なお、今回の研究成果は、米国サンフランシスコで2017年2月5日より開催されている「国際固体素子回路会議(ISSCC 2017)」で、その詳細を発表した。

Copyright © ITmedia, Inc. All Rights Reserved.

関連記事

32G対応の衝撃検知に適した小型加速度センサー

32G対応の衝撃検知に適した小型加速度センサー

ロームグループのKionixが、衝撃検知に適した小型加速度センサー「KX222/KX224」を販売する。±8G、±16G、±32Gと3つの検出範囲を備えており、産業機器の衝撃検知などにも利用できる。 高速マシンビジョンなどに適した、48Mピクセル 35ミリCMOSセンサー

高速マシンビジョンなどに適した、48Mピクセル 35ミリCMOSセンサー

CMOSISが、48Mピクセル グローバルシャッター搭載CMOSイメージセンサー「CMV50000」のサンプル出荷を開始した。8Kモードであっても最大30fps出力可能で、高速マシンビジョンやテレビカメラなどの用途に適する。 消費電流1.6mA以下のホールセンサー、車載・産業・家電向けに展開

消費電流1.6mA以下のホールセンサー、車載・産業・家電向けに展開

インフィニオンテクノロジーズは、消費電流1.6mA以下のホールセンサー「TLx496x」ファミリーを発表した。 フットプリント4×1.75mmの光センサーモジュール

フットプリント4×1.75mmの光センサーモジュール

amsは2016年8月、カラー(RGB)、照度、近接センサーを組み合わせた光センサーモジュール「TMD3700」を発表した。フットプリントは4.00×1.75mm、外形高さは1.00mmである。 8×8画素サーモパイル型赤外線アレイセンサーモジュール

8×8画素サーモパイル型赤外線アレイセンサーモジュール

セイコーNPCは、遠赤外線用Siレンズ光学系と検出回路、制御用MCUを1つの基板上に実装した、8×8画素サーモパイル型赤外線アレイセンサーモジュール「SMH-01B01」を開発した。